# **inter<sub>s</sub>i**l<sup>®</sup>

# Radiation Hardened, SEE Hardened, Non-Inverting, Quad CMOS Driver

# ISL7457SRH

The ISL7457SRH is a radiation hardened, SEE hardened, high speed, non-inverting, quad CMOS driver. It is capable of running at clock rates up to 40MHz and features 2A typical peak drive capability and a nominal on-resistance of just  $3.5\Omega$ . The ISL7457SRH is ideal for driving highly capacitive loads, such as storage and vertical clocks in CCD applications. It is also well suited to level-shifting and clock-driving applications.

Each output of the ISL7457SRH can be switched to either the high (V<sub>H</sub>) or low (V<sub>L</sub>) supply pins, depending on the related input pin. The inputs are compatible with both 3.3V and 5V CMOS logic. The output enable (OE) pin can be used to put the outputs into a high-impedance state. This is especially useful in CCD applications, where the driver should be disabled during power down.

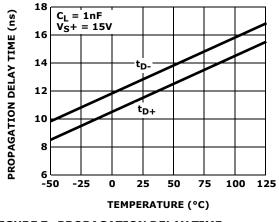

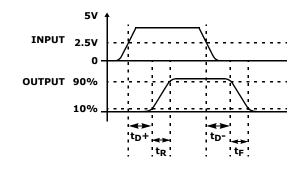

The ISL7457SRH also features very fast rise and fall times which are typically matched to within 1ns. The propagation delay is also matched between rising and falling edges to typically within 1.5ns.

The ISL7457SRH is available in a 16 lead ceramic flatpack package and specified for operation over the full -55°C to +125°C ambient temperature range.

#### Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed here must be used when ordering.

Detailed Electrical Specifications for these devices are contained in SMD 5962-08230. A "hot-link" is provided on our website for downloading.

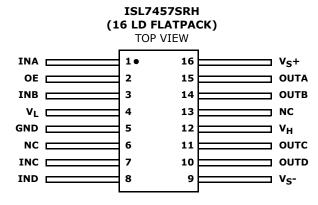

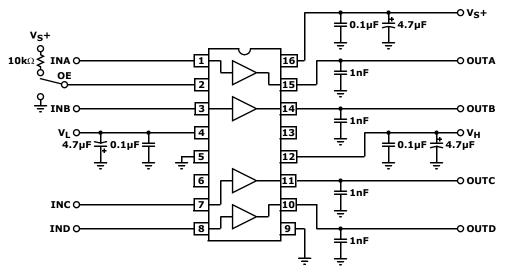

# **Pin Configuration**

# **Features**

- Electrically Screened to SMD 5962-08230

- QML Qualified per MIL-PRF-38535 Requirements

- Full Mil-temp Range Operation  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$

- Radiation Hardness

- TID [50-300 rad(Si)/s]....10krad(Si) min

- SEE Hardness

- LET (SEL and SEB Immunity)40MeV/mg/cm<sup>2</sup> min

- LET [SET =  $\Delta V_{OUT}$  < 15V,  $\Delta t$  < 500ns].... 40MeV/mg/cm<sup>2</sup>

- 4 Channels

- Clocking Speeds up to 40MHz

- 11ns/12ns Typical  $t_{\mbox{\scriptsize R}}/t_{\mbox{\scriptsize F}}$  with 1nF Load (15V bias)

- 1ns Typical Rise and Fall Time Match (15V bias)

- 1.5ns Typical Prop Delay Match (15V bias)

- Low Quiescent Current < 1mA Typical

- Fast Output Enable Function 12ns Typical (15V bias)

- Wide Output Voltage Range

- $0V \le V_L \le 8V$

- 2.5V  $\leq V_{H} \leq 16.5V$

- 2A Typical Peak Drive Current (15V Bias)

- $3.5\Omega$  Typical ON-Resistance (15V bias)

- Input Level Shifters

- 3.3V/5V CMOS Compatible Inputs

# **Applications**

CCD Drivers, Clock/line Drivers, Level-Shifters

# **Ordering Information**

| ORDERING NUMBER    | PART NUMBER        | TEMP. RANGE<br>(°C) | PACKAGE        | PKG.<br>DWG. # |

|--------------------|--------------------|---------------------|----------------|----------------|

| 5962D0823001QXC    | ISL7457SRHQF       | -55 to +125         | 16 Ld Flatpack | K16.A          |

| 5962D0823001VXC    | ISL7457SRHVF       | -55 to +125         | 16 Ld Flatpack | K16.A          |

| 5962D0823001V9A    | ISL7457SRHVX       | -55 to +125         | Die            |                |

| ISL7457SRHF/PROTO  | ISL7457SRHF/PROTO  | -55 to +125         | 16 Ld Flatpack | K16.A          |

| ISL7457SRHX/SAMPLE | ISL7457SRHX/SAMPLE | -55 to +125         | Die            |                |

# **Electrical Specifications** Typical values reflect $V_S$ + = $V_H$ = 5V, $V_S$ - = $V_L$ = 0V, OE = $V_S$ +, $T_A$ = +25°C unless otherwise specified.

| PARAMETER            | DESCRIPTION                                 | CONDITION                                                                 | MIN | ТҮР  | MAX | UNIT |

|----------------------|---------------------------------------------|---------------------------------------------------------------------------|-----|------|-----|------|

| INPUT                | 1                                           |                                                                           |     | 1    |     | L    |

| V <sub>IH</sub>      | Logic "1" Input Voltage                     |                                                                           |     | 1.3  |     | V    |

| I <sub>IH</sub>      | Logic "1" Input Current                     | $INx = V_S +$                                                             |     | 10   |     | nA   |

| V <sub>IL</sub>      | Logic "0" Input Voltage                     |                                                                           |     | 1.23 |     | V    |

| I <sub>IL</sub>      | Logic "0" Input Current                     | INx = 0V                                                                  |     | -5   |     | nA   |

| C <sub>IN</sub>      | Input Capacitance                           |                                                                           |     | 5.7  |     | pF   |

| R <sub>IN</sub>      | Input Resistance                            |                                                                           |     | 500  |     | MΩ   |

| OUTPUT               |                                             |                                                                           |     |      | 1   |      |

| R <sub>OH</sub>      | ON Resistance V <sub>H</sub> to OUTx        | $INx = V_S+$ , $I_{OUTx} = -100 mA$                                       |     | 8    |     | Ω    |

| R <sub>OL</sub>      | ON Resistance V <sub>L</sub> to OUTx        | $INx = 0V, I_{OUTx} = +100mA$                                             |     | 6    |     | Ω    |

| I <sub>LEAK+</sub>   | Positive Output Leakage Current             | $INx = V_S+$ , $OE = 0V$ , $OUTx = V_S+$                                  |     | 5    |     | nA   |

| I <sub>LEAK-</sub>   | Negative Output Leakage Current             | $INx = V_S+, OE = 0V, OUTx = V_S-$                                        |     | -5   |     | nA   |

| POWER SUPP           | PLY                                         |                                                                           |     |      | 1   |      |

| I <sub>S+</sub>      | V <sub>S</sub> + Supply Current             | $INx = 0V and V_S+$                                                       |     | 0.2  |     | mA   |

| I <sub>S-</sub>      | V <sub>S</sub> - Supply Current             | $INx = 0V and V_S +$                                                      |     | -0.2 |     | mA   |

| IH                   | V <sub>H</sub> Supply Current               | $INx = 0V and V_S+$                                                       |     | 0.1  |     | μA   |

| IL                   | V <sub>L</sub> Supply Current               | $INx = 0V and V_S+$                                                       |     | 0.1  |     | μA   |

| SWITCHING            | CHARACTERISTICS                             |                                                                           |     |      | P.  |      |

| t <sub>R</sub>       | Rise Time                                   | INx = 0V to 4.5V step, $C_L = 1nF$                                        |     | 23   |     | ns   |

| t <sub>F</sub>       | Fall Time                                   | INx = 4.5V to 0V step, $C_L = 1nF$                                        |     | 20   |     | ns   |

| $t_{RF\Delta}$       | t <sub>R</sub> , t <sub>F</sub> Mismatch    | $C_L = 1nF$                                                               |     | 3    |     | ns   |

| t <sub>D</sub> +     | Turn-On Delay Time                          | INx = 0V to 4.5V step, $C_L = 1nF$                                        |     | 20   |     | ns   |

| t <sub>D</sub> -     | Turn-Off Delay Time                         | INx = 4.5V to 0V step, $C_L = 1nF$                                        |     | 22   |     | ns   |

| t <sub>DD</sub>      | t <sub>D</sub> +, t <sub>D</sub> - Mismatch | C <sub>L</sub> = 1nF                                                      |     | 2    |     | ns   |

| t <sub>ENABLE</sub>  | Enable Delay Time                           | INx = V <sub>S</sub> +, OE = 0V to 4.5V step, R <sub>L</sub> = $1k\Omega$ |     | 21   |     | ns   |

| t <sub>DISABLE</sub> | Disable Delay Time                          | INx = V <sub>S</sub> +, OE = 4.5V to 0V step, $R_L = 1k\Omega$            |     | 46   |     | ns   |

**Electrical Specifications** Typical values reflect  $V_S$ + =  $V_H$  = 15V,  $V_{S^-}$  =  $V_L$ = 0V, OE =  $V_S$ +,  $T_A$  = +25°C unless otherwise specified.

| PARAMETER            | DESCRIPTION                                 | CONDITION                                                               | MIN | ТҮР  | MAX | UNIT     |

|----------------------|---------------------------------------------|-------------------------------------------------------------------------|-----|------|-----|----------|

| INPUT                |                                             |                                                                         |     |      | I   | <u>.</u> |

| V <sub>IH</sub>      | Logic "1" Input Voltage                     |                                                                         |     | 1.63 |     | V        |

| I <sub>IH</sub>      | Logic "1" Input Current                     | $INx = V_S +$                                                           |     | 10   |     | nA       |

| V <sub>IL</sub>      | Logic "0" Input Voltage                     |                                                                         |     | 1.4  |     | V        |

| I <sub>IL</sub>      | Logic "0" Input Current                     | INx = 0V                                                                |     | -5   |     | nA       |

| C <sub>IN</sub>      | Input Capacitance                           |                                                                         |     | 5.7  |     | pF       |

| R <sub>IN</sub>      | Input Resistance                            |                                                                         |     | 1.5  |     | GΩ       |

| OUTPUT               |                                             |                                                                         |     |      | 1   |          |

| R <sub>OH</sub>      | ON Resistance V <sub>H</sub> to OUTx        | $INx = V_S+$ , $I_{OUTx} = -100 mA$                                     |     | 3.5  |     | Ω        |

| R <sub>OL</sub>      | ON Resistance $V_L$ to OUTx                 | $INx = 0V, I_{OUTx} = +100 \text{mA}$                                   |     | 3    |     | Ω        |

| I <sub>LEAK+</sub>   | Positive Output Leakage Current             | $INx = V_S+, OE = 0V, OUTx = V_S+$                                      |     | 15   |     | nA       |

| I <sub>LEAK</sub> -  | Negative Output Leakage Current             | $INx = V_S+$ , $OE = 0V$ , $OUTx = V_S-$                                |     | -15  |     | nA       |

| POWER SUPP           | PLY                                         |                                                                         |     |      | 1   |          |

| I <sub>S+</sub>      | V <sub>S</sub> + Supply Current             | $INx = 0V and V_S +$                                                    |     | 0.8  |     | mA       |

| I <sub>S-</sub>      | V <sub>S</sub> - Supply Current             | $INx = 0V and V_S+$                                                     |     | -0.8 |     | mA       |

| I <sub>H</sub>       | V <sub>H</sub> Supply Current               | $INx = 0V and V_S+$                                                     |     | 0.1  |     | μA       |

| IL                   | V <sub>L</sub> Supply Current               | $INx = 0V and V_S +$                                                    |     | 0.1  |     | μΑ       |

| SWITCHING            | CHARACTERISTICS                             |                                                                         |     |      |     |          |

| t <sub>R</sub>       | Rise Time                                   | $INx = 0V \text{ to } 5V \text{ step}, C_L = 1nF$                       |     | 11   |     | ns       |

| t <sub>F</sub>       | Fall Time                                   | INx = 5V to 0V step, $C_L = 1nF$                                        |     | 12   |     | ns       |

| $t_{RF\Delta}$       | t <sub>R</sub> , t <sub>F</sub> Mismatch    | $C_L = 1nF$                                                             |     | 1    |     | ns       |

| t <sub>D</sub> +     | Turn-On Delay Time                          | INx = 0V to 5V step, $C_L = 1nF$                                        |     | 11.5 |     | ns       |

| t <sub>D</sub> -     | Turn-Off Delay Time                         | INx = 5V to 0V step, $C_L = 1nF$                                        |     | 13   |     | ns       |

| t <sub>DD</sub>      | t <sub>D</sub> +, t <sub>D</sub> - Mismatch | $C_L = 1nF$                                                             |     | 1.5  |     | ns       |

| t <sub>ENABLE</sub>  | Enable Delay Time                           | INx = V <sub>S</sub> +, OE = 0V to 5V step, R <sub>L</sub> = $1k\Omega$ |     | 12   |     | ns       |

| t <sub>DISABLE</sub> | Disable Delay Time                          | INx = V <sub>S</sub> +, OE = 5V to 0V step, $R_L = 1k\Omega$            |     | 27   |     | ns       |

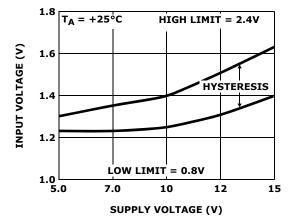

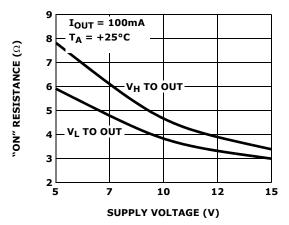

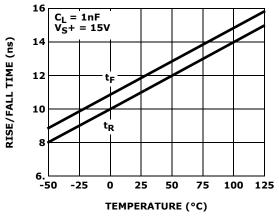

# **Typical Performance Curves (Pre-rad)**

FIGURE 1. SWITCH THRESHOLD vs SUPPLY VOLTAGE

FIGURE 3. "ON"-RESISTANCE vs SUPPLY VOLTAGE

FIGURE 5. RISE/FALL TIME vs TEMPERATURE

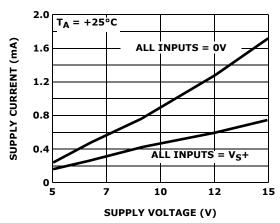

FIGURE 2. QUIESCENT SUPPLY CURRENT vs SUPPLY VOLTAGE

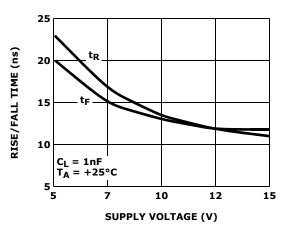

FIGURE 4. RISE/FALL TIME vs SUPPLY VOLTAGE

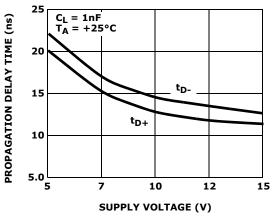

FIGURE 6. PROPAGATION DELAY TIME vs SUPPLY VOLTAGE

# Typical Performance Curves (Pre-rad) (Continued)

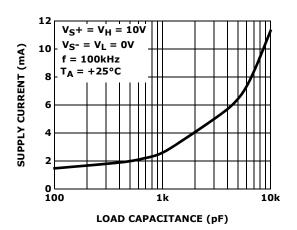

FIGURE 9. SUPPLY CURRENT PER CHANNEL vs LOAD CAPACITANCE

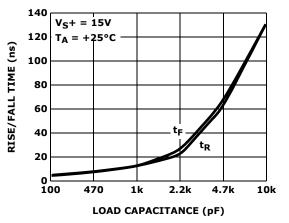

FIGURE 8. RISE/FALL TIME vs LOAD CAPACITANCE

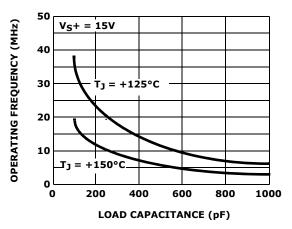

FIGURE 10. OPERATING FREQUENCY vs LOAD CAPACITANCE DERATING CURVES

TABLE 1. OPERATING VOLTAGE RANGE

| PIN                     | MIN                     | МАХ              |

|-------------------------|-------------------------|------------------|

| $V_{S}$ + to $V_{S}$ -  | 4.5V                    | 16.5V            |

| V <sub>S</sub> - to GND | 0V                      | 0V               |

| V <sub>H</sub>          | V <sub>S</sub> - + 2.5V | V <sub>S</sub> + |

| VL                      | V <sub>S</sub> -        | V <sub>S</sub> + |

| $V_{H}$ to $V_{L}$      | 0V                      | 16.5V            |

| $V_L$ to $V_S$ -        | 0V                      | 8V               |

# **Timing Diagram**

# **Standard Test Configuration**

# **Pin Descriptions**

| 16 LD FLATPACK | NAME             | FUNCTION                | EQUIVALENT CIRCUIT                                                                               |

|----------------|------------------|-------------------------|--------------------------------------------------------------------------------------------------|

| 1              | INA              | Input Channel A         | $V_{S^+}$                                                                                        |

| 2              | OE               | Output enable           | (Reference Circuit 1)                                                                            |

| 3              | INB              | Input Channel B         | (Reference Circuit 1)                                                                            |

| 4              | VL               | Low voltage input pin   |                                                                                                  |

| 5              | GND              | Input logic ground      |                                                                                                  |

| 6, 13          | NC               | No connection           |                                                                                                  |

| 7              | INC              | Input Channel C         | (Reference Circuit 1)                                                                            |

| 8              | IND              | Input Channel D         | (Reference Circuit 1)                                                                            |

| 9              | V <sub>S</sub> - | Negative supply voltage |                                                                                                  |

| 10             | OUTD             | Output Channel D        | $O V_H$<br>$V_{S^+}$<br>$V_{S^-}$<br>$V_{S^-}$<br>$V_{S^-}$<br>$V_{S^-}$<br>$O V_L$<br>CIRCUIT 2 |

| 11             | OUTC             | Output Channel C        | (Reference Circuit 2)                                                                            |

| 12             | V <sub>H</sub>   | High voltage input pin  |                                                                                                  |

| 14             | OUTB             | Output Channel B        | (Reference Circuit 2)                                                                            |

| 15             | OUTA             | Output Channel A        | (Reference Circuit 2)                                                                            |

| 16             | V <sub>S</sub> + | Positive supply voltage |                                                                                                  |

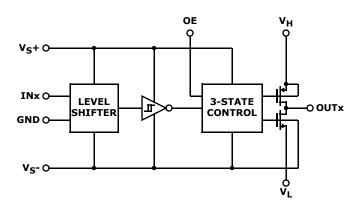

# **Block Diagram**

# **Application Information**

#### **Product Description**

The ISL7457SRH is a high performance, high speed quad CMOS driver. Each channel of the ISL7457SRH consists of a single P-channel high side driver and a single N-Channel low side driver. These  $3.5\Omega$  devices will pull the output (OUTx) to either the high or low voltage, on  $V_{\rm H}$  and  $V_{\rm L}$  respectively, depending on the input logic signal (INx). It should be noted that there is only one set of high and low voltage pins.

A common output enable (OE) pin is available on the ISL7457SRH. When this pin is pulled low, it will put all outputs in a high impedance state.

#### Supply Voltage Range and Input Compatibility

The ISL7457SRH is designed to operate on nominal 5V to 15V supplies with  $\pm 10\%$  tolerance. Table 1 on page 7 shows the specifications for the relationship between the V<sub>S</sub>+, V<sub>S</sub>-, V<sub>H</sub>, V<sub>L</sub>, and GND pins. The ISL7457SRH does not contain a true analog switch and therefore V<sub>L</sub> should always be less than V<sub>H</sub>.

All input pins are compatible with both 3.3V and 5V CMOS signals.

#### **PCB Layout Guidelines**

1. A ground plane must be used, preferably located on layer #2 of the PCB.

2. Connect the GND and  $\ensuremath{\mathsf{V}}_{S}\xspace$  pins directly to the ground plane.

2. The V<sub>S</sub>+, V<sub>H</sub> and V<sub>L</sub> pins should be bypassed directly to the ground plane using a low-ESR,  $4.7\mu F$  solid tantalum capacitor in parallel with a  $0.1\mu F$  ceramic capacitor. Locate all bypass capacitors as close as possible to the respective pins of the IC.

3. Keep all input and output connections to the IC as short as possible.

4. For high frequency operation above 1MHz, consider use of controlled impedance traces terminated into  $50\Omega$  on all inputs and outputs.

#### **Power Dissipation Calculation**

When switching at high speeds, or driving heavy loads, the ISL7457SRH drive capability is limited by the rise in die temperature brought about by internal power dissipation. For reliable operation die temperature must be kept below  $T_{JMAX}$  (+150°C).

Power dissipation may be calculated as shown in Equation 1:

$$P_{D} = (V_{S} \times I_{S}) + \sum_{1}^{1} (C_{INT} \times V_{S}^{2} \times f) + (C_{L} \times V_{OUT}^{2} \times f)$$

(EQ. 1)

where:

$P_D$  is the power dissipated in the device.

$V_{S}$  is the total power supply to the ISL7457SRH (from  $V_{S}+$  to  $V_{S}\text{-}).$

$\mathrm{I}_{S}$  is the quiescent supply current.

$C_{INT}$  is the internal load capacitance (80pF max).

f is the operating frequency.

C<sub>L</sub> is the load capacitance.

$V_{OUT}$  is the swing on the output ( $V_H$  -  $V_L$ ).

#### **Junction Temperature Calculation**

Once the power dissipation for the application is determined, the maximum junction temperature can be calculated as shown in Equation 2:

$$T_{JMAX} = T_{SMAX} + (\Theta_{JC} + \Theta_{CS}) \times P_{D}$$

(EQ. 2)

where:

$T_{JMAX}$  is the maximum operating junction temperature (+150°C).

$\mathsf{T}_{\mathsf{SMAX}}$  is the maximum operating sink temperature of the PCB.

$\theta_{JC}$  is the thermal resistance, junction-to-case, of the package.

$\theta_{CS}$  is the thermal resistance, case-to-sink, of the PCB.

$\mathsf{P}_\mathsf{D}$  is the power dissipation calculated in Equation 1.

#### **PCB Thermal Management**

To minimize the case-to-sink thermal resistance, it is recommended that multiple vias be placed on the top layer of the PCB directly underneath the IC. The vias should be connected to the ground plane, which functions as a heatsink. A gap filler material (i.e. a Sil-Pad or thermally conductive epoxy) may be used to insure good thermal contact between the bottom of the IC and the vias.

### ISL7457SRH

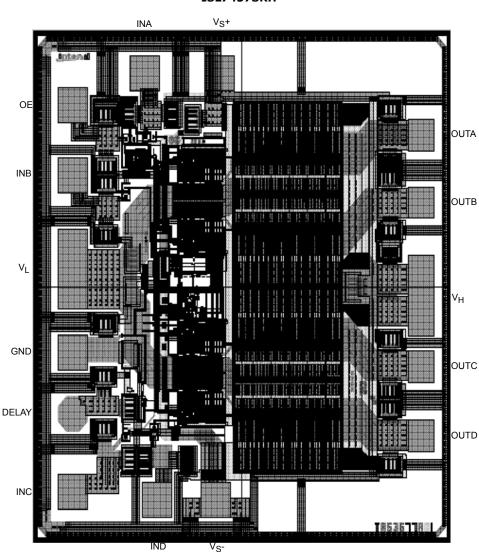

# **Die Characteristics**

#### **DIE DIMENSIONS:**

2390µm x 2445µm (94.1 mils x 96.3 mils) Thickness:13.0 mils  $\pm 0.5$  mil

#### **INTERFACE MATERIALS**

#### Glassivation

Type: PSG and Silicon Nitride Thickness: 0.5 $\mu$ m ± 0.05 $\mu$ m to 0.7  $\mu$ m ±0.05 $\mu$ m

#### **Top Metallization**

Type: AlCuSi (1%/0.5%) Thickness: 1.0 µm ±0.1µm

#### Substrate:

Type: Silicon Isolation: Junction

#### **Backside Finish:**

Silicon

#### ASSEMBLY RELATED INFORMATION

#### Substrate Potential:

Vs-

#### ADDITIONAL INFORMATION

#### Worst Case Current Density:

< 2 x  $10^5$  A/cm<sup>2</sup> (See Figure 10)

#### **Transistor Count:**

1142

## **Metallization Mask Layout**

#### ISL7457SRH

### **Layout Characteristics**

Step and Repeat: 2390µm x 2445µm

The DELAY pad is not bonded.

#### TABLE 1. LAYOUT X-Y COORDINATES

| PAD NAME         | Χ<br>(μm) | ۲<br>(µm) | DX<br>(µm) | DY<br>(µm) | PROBES<br>PER PAD |

|------------------|-----------|-----------|------------|------------|-------------------|

| IND              | 675       | 190       | 140        | 140        | 1                 |

| V <sub>S</sub> - | 995       | 190       | 140        | 140        | 1                 |

| OUTD             | 2118      | 490       | 122        | 133        | 1                 |

| OUTC             | 2118      | 795       | 122        | 133        | 1                 |

| V <sub>H</sub>   | 2118      | 1039      | 122        | 345        | 2                 |

|                  | 2118      | 1211      |            |            |                   |

| OUTB             | 2118      | 1554      | 122        | 133        | 1                 |

| OUTA             | 2118      | 1861      | 122        | 133        | 1                 |

| V <sub>S</sub> + | 1015      | 2140      | 140        | 140        | 1                 |

| INA              | 608       | 2140      | 140        | 140        | 1                 |

| OE               | 213       | 1993      | 140        | 140        | 1                 |

| INB              | 213       | 1673      | 140        | 140        | 1                 |

| VL               | 213       | 1331      | 140        | 345        | 2                 |

|                  | 213       | 1159      |            |            |                   |

| GND              | 213       | 864       | 140        | 140        | 1                 |

| DELAY            | 213       | 585       | 140        | 140        | 0                 |

| INC              | 213       | 213       | 140        | 140        | 1                 |

For additional products, see <a href="https://www.intersil.com/product\_tree">www.intersil.com/product\_tree</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at <u>www.intersil.com/design/quality</u>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

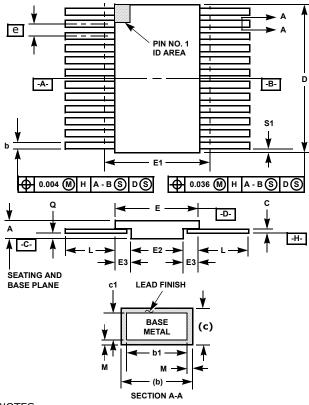

#### Ceramic Metal Seal Flatpack Packages (Flatpack)

#### NOTES:

- 1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark. Alternately, a tab (dimension k) may be used to identify pin one.

- 2. If a pin one identification mark is used in addition to a tab, the limits of dimension k do not apply.

- 3. This dimension allows for off-center lid, meniscus, and glass overrun.

- 4. Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness. The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- 5. N is the maximum number of terminal positions.

- 6. Measure dimension S1 at all four corners.

- 7. For bottom-brazed lead packages, no organic or polymeric materials shall be molded to the bottom of the package to cover the leads.

- Dimension Q shall be measured at the point of exit (beyond the meniscus) of the lead from the body. Dimension Q minimum shall be reduced by 0.0015 inch (0.038mm) maximum when solder dip lead finish is applied.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH

| K16.A MIL-STD-1835 CDFP4-F16 (F-5A, CONFIGURATION B) |

|------------------------------------------------------|

| 16 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE          |

| SYM- | INCHES |        | MILLIMETERS |       | NOTE |  |

|------|--------|--------|-------------|-------|------|--|

| BOL  | MIN    | MAX    | MIN         | MAX   | S    |  |

| А    | 0.045  | 0.115  | 1.14        | 2.92  | -    |  |

| b    | 0.015  | 0.022  | 0.38        | 0.56  | -    |  |

| b1   | 0.015  | 0.019  | 0.38        | 0.48  | -    |  |

| С    | 0.004  | 0.009  | 0.10        | 0.23  | -    |  |

| c1   | 0.004  | 0.006  | 0.10        | 0.15  | -    |  |

| D    | -      | 0.440  | -           | 11.18 | 3    |  |

| Е    | 0.245  | 0.285  | 6.22        | 7.24  | -    |  |

| E1   | -      | 0.315  | -           | 8.00  | 3    |  |

| E2   | 0.130  | -      | 3.30        | -     | -    |  |

| E3   | 0.030  | -      | 0.76        | -     | 7    |  |

| е    | 0.050  | ) BSC  | 1.27        | 7 BSC | -    |  |

| k    | 0.008  | 0.015  | 0.20        | 0.38  | 2    |  |

| L    | 0.250  | 0.370  | 6.35        | 9.40  | -    |  |

| Q    | 0.026  | 0.045  | 0.66        | 1.14  | 8    |  |

| S1   | 0.005  | -      | 0.13        | -     | 6    |  |

| М    | -      | 0.0015 | -           | 0.04  | -    |  |

| Ν    | 1      | 6      | :           | 16    | -    |  |

Rev. 1 2-20-95